- Mux 4x1 verilog programme by using 2x1 test bench how to#

- Mux 4x1 verilog programme by using 2x1 test bench generator#

- Mux 4x1 verilog programme by using 2x1 test bench series#

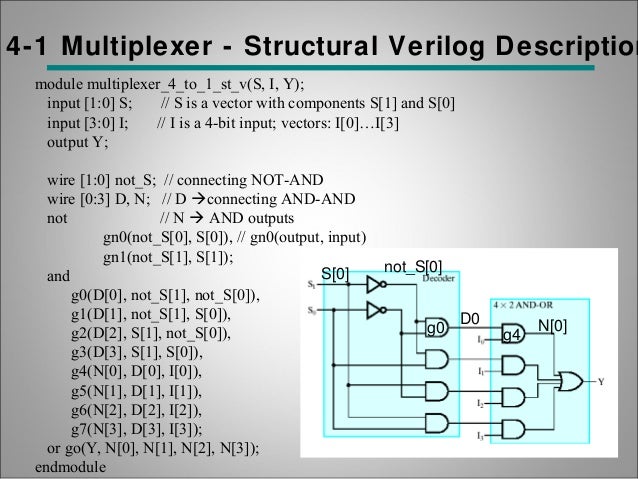

4 bit Ripple Carry Adder using basic logic gates.Positive edge triggered JK Flip Flop with reset input.

Mux 4x1 verilog programme by using 2x1 test bench series#

Mux 4x1 verilog programme by using 2x1 test bench how to#

How to test your design without writing a seperate.Reading and Writing files in VHDL - An easy way of.

Mux 4x1 verilog programme by using 2x1 test bench generator#

Examples (38) vhdl tips (38) useful codes (31) Behavior level model (11) xilinx tips (10) xilinx errors (8) testbench (7) Gate level model (6) core generator (6) state machine (6) synthesisable (6) block RAM (5) file handling (5) fixed point package (4) port mapping (4) video tutorials (4) arrays and records (3) delay (3) flipflops (3) functions (3) interview Q's (3) real variable (3) BCD (2) Xilinx (2) adders (2) coding style (2) counters (2) generate (2) generic (2) gray code (2) image processing (2) modelsim (2) multipliers (2) random number generator (2) resets (2) vivado (2) xilinx isim (2) 7 segment display (1) BCD converter (1) Buffers (1) C and VHDL (1) CRC (1) FFT (1) FIFO (1) FIR filter (1) Frequency measurement (1) LFSR (1) QSD (1) coe file (1) comparator (1) debouncing (1) digital clock (1) distributed RAM (1) dual port ram (1) error (1) fast adder (1) floating point (1) for loop (1) frequency multiplier (1) gated clock (1) hexadecimal (1) ieee_proposed (1) matrix multiplier (1) memory (1) numeric_std (1) package (1) pipelining (1) polynomial equation (1) power reduction (1) quaternary (1) sensitivity list (1) sequence detector (1) serial (1) signals (1) simulation tool (1) square root (1) stack (1) textio (1) unsigned (1) variables (1) vhdl beginners guide (1) vhdl language (1) wait for (1)

0 kommentar(er)

0 kommentar(er)